In edge triggering output can change only at one instant during the lock cycle with level clocking output can changeĭuring an entire half cycle of the clock. Of level-clocked, the output can change when the clock is high (or low).Ģ. When a circuit is edge triggered the output can change only on the rrising or falling edge of the clock. D flip flops are also used in finite state machines.ġ. FPGA contains edge triggered flip flops.ħ. Many logic synthesis tool use only D flip flop or D latch.Ħ. The output being synchronized to a clock.ĥ. Flip flop can be considered as a basic memory cell because it stores the value on the data line with the advantage of Latches are used as temporary buffers whereas flip flops are used as registers.Ĥ. Power consumption in Flip flop is more as compared to D latch.ģ. The disadvantage of the D FF is its circuit size, which is about twice as large as that of a D latch. D-latch is a level Triggering device while D Flip Flop is an Edge triggering device.Ģ.

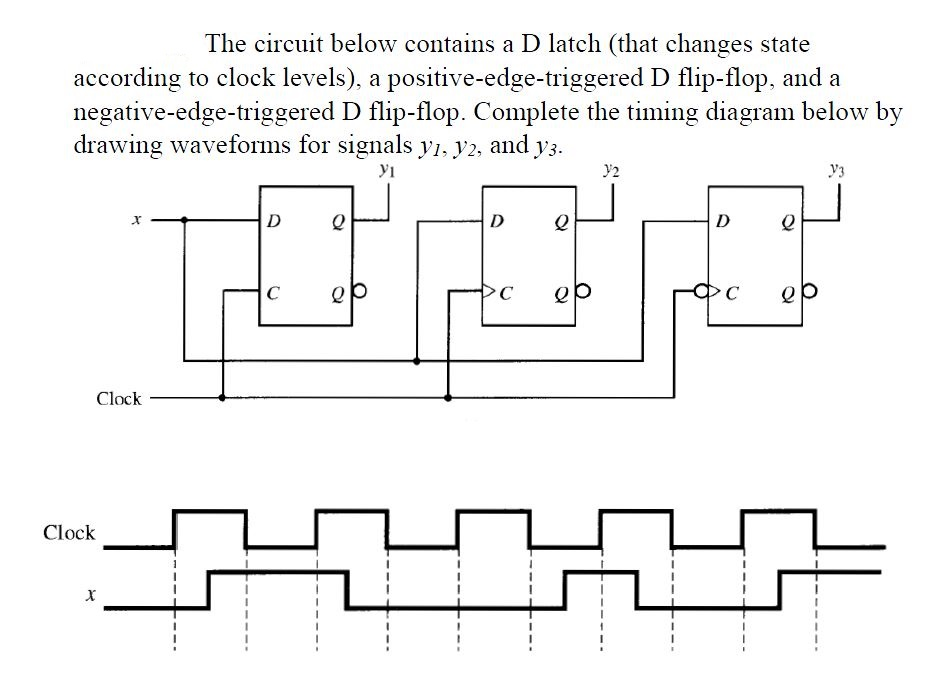

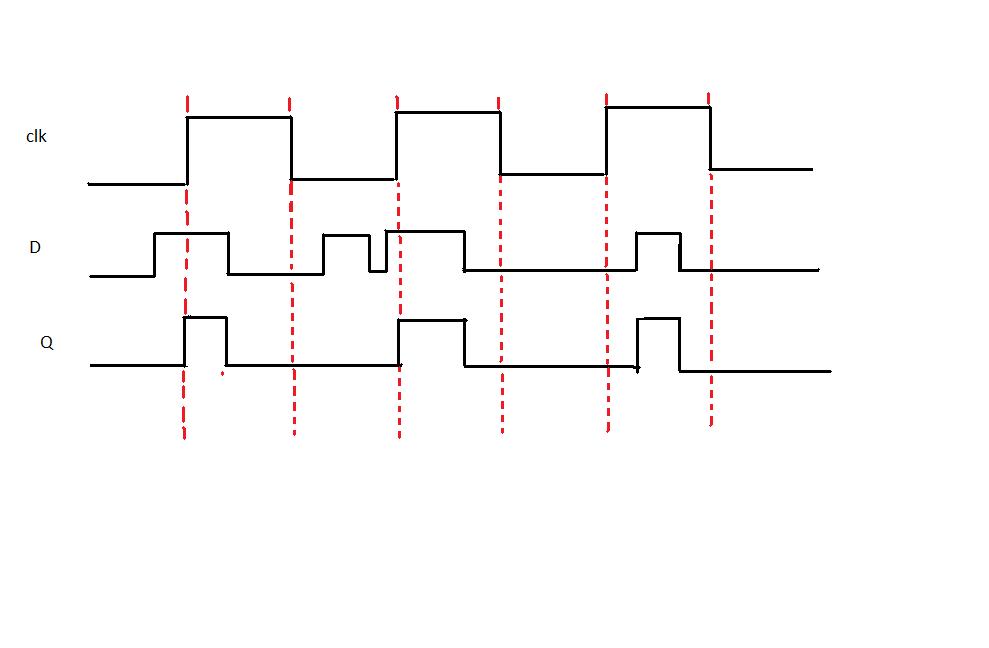

The advantage of the D flip-flop over the D-type "transparent latch" is that the signal on the D input pin is captured the moment the flip-flop is clocked, and subsequent changes on the D input will be ignored until the next clock event.įrom the timing diagram it is clear that the output Q changes only at the positive edge.At each positive edge the output Q becomes equal to the input D at that instant and this value of Q is held untill the next positive edgeĬharacteristics and applications of D latch and D Flip Flop :ġ. The D FlipFlop can be interpreted as a delay line or zero order hold.

The flip-flop is positive edge triggered, which is shown on the CK input in Fig. That's why, it is commonly known as a delay flip flop. Construct timing diagrams to explain the operation of D Type flip-flops. The working of D flip flop is similar to the D latch except that the output of D Flip Flop takes the state of the D input at the moment of a positive edge at the clock pin (or negative edge if the clock input is active low) and delays it by one clock cycle.

When the CLK input falls to logic 0, the last state of the D input is trapped and held in the latch.įrom the timing diagram it is clear that the output Q's waveform resembles that of input D's waveform when the clock is high whereas when the clock is low Q retains the previous value of D (the value before clock dropped down to 0) If the data on the D line changes state while the clock pulse is high, then the output, Q, follows the input, D. Thus depending on the implementation, a D-type flip-flops clock input may be positive-edge or negative-edge triggered. Lets compare timing diagrams for a normal D latch versus one that is edge-triggered. The D latch is used to capture, or 'latch' the logic level which is present on the Data line when the clock input is high. Latch is an electronic device that can be used to store one bit of information.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed